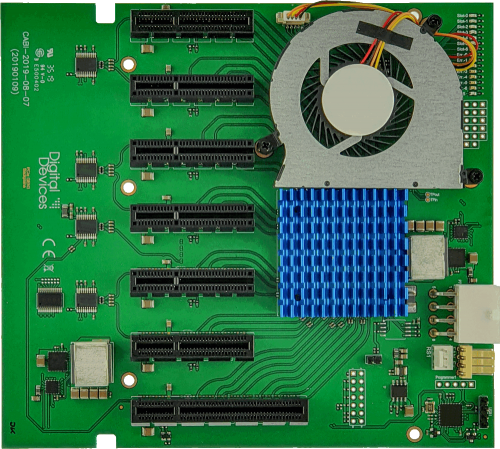

Unsere Backplanes erweitern die Anzahl der PCIe-Steckplätze für ein Hostsystem.

Die Backplane verfügt über einen transparenten PCIe-Switch, der die Kommunikation zwischen den PCIe-Geräten und dem Host transparent abwickelt.

Es werden keine Treiber benötigt und die Funktionalität ist auf allen Systemen von Windows über MAC OS bis Linux gewährleistet.

Die Backplane PCIe Gen3 6-fach verfügt über eine 64 Gbit/s Uplink (X8) und über sechs 32 Gbit/s Downlinks (X4).

Über USB kann der Status abgefragt/dargestellt werden.

Die Backplane ist passend für die Gehäuse Case #2, Case #3 und Case #4.

3 Einsatzmöglichkeiten dieser Backplane:

- Mit einem Clientadapter im Upstream Port einer Backplane und einem Hostadapter (via mini DP Kabel) wird die Verbindung zu einem freien PCIe Slot im Host PC/System hergestellt. Dies kann ein PCIe Slot mit 4 oder 8 Lanes, ein M2.M oder ein M2.E Slot sein. Host- und Client-Adapter passen sich automatisch an die Kabellänge an (0,5 bis 7 m). Die Backplane stellt dem Hostsystem 6 weitere PCIe Slots transparent zur Verfügung.

- Mit Thunderbold Adapter direkt an eines der folgenden bestehenden Systeme: Apple/PC/Hostsystem/Notebook. Die Backplane stellt dem Host PC/Notebook 6 PCIe Slots zur Verfügung.

- Mit PCIe CPU Board als stand-alone System. Die Backplane stellt dem PCIe CPU Board 6 PCIe Slots zur Verfügung.

Hervorragend geeignet für:

- Industrielle Automatisierung

- Ersatz für teure PICMG 1.3 basierend CPU Boards und Backplanes durch Standard Industrie Mainboards + PCIE Expansion und Gehäuse

- Ersatz für teure PXI basierende Messsysteme durch Standard Industrie PC + PCIE Expansion

- Messgeräte

- PCIe Entwicklung

- Web Hosting

- Apple Thunderbold/PCIe Erweiterung

- Notebook Thunderbold/PCIe Erweiterung

- Upstream: 1x PCI Express 3.0 X8

- Downstream: 6x PCI Express 3.0 X4

- Switching Kapazität: 58 Gbps Power

- Leistungsaufnahme: 15 W

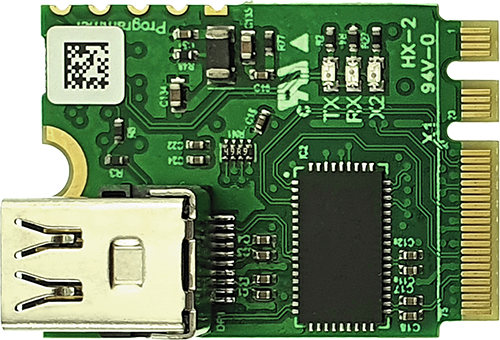

- USB-Anschluss

- Passend für die Gehäuse Case #2, Case #3 und Case #4

- Hergestellt in Deutschland

| Erzielbare Datenraten | Kabel 1 | + Kabel 2 | + Kabel 3+4 |

| PCIe Generation1 | 5 Gbit/s | 10 Gbit/s | 20 Gbit/s |

| PCIe Generation2 | 10 Gbit/s | 20 Gbit/s | 40 Gbit/s |

| PCIe Generation3 | 16 Gbit/s | 32 Gbit/s | 64 Gbit/s |

Die Backplane ermöglicht via USB Interface Diagnose und Debug Informationen.

Die API stellt folgende Informationen zur Verfügung:

- Leistungsverbrauch

- Stromaufnahme der 12 V und 3V3 Schiene

- PCIe Link Status

- Temperatur

- Lüfter Status

- Augendiagramm

- PCIe Slot Einstellungen.

Für die PCIe Entwicklung stehen u. a. bereit:

- Transaction Layer Packet (TLP) generator for testing and debugging of links and error handling

- Real-time eye capture

- Any-to-any port mirroring for debug purposes

- External loopback at PHY and TLP layers

- Errors, statistics, performance, and TLP latency counters

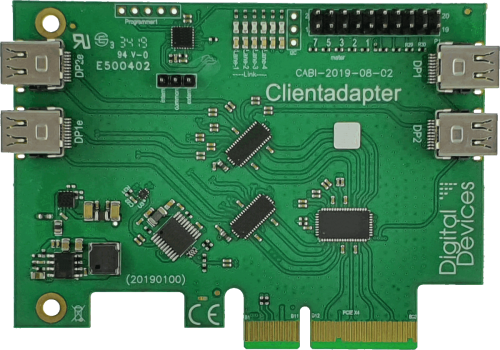

Clientadapter X4 Intern/Extern

- bis zu 4 PCIe Lanes, 32 Gbit/s

- für Anwendungen inner- und außerhalb des Gehäuses

mehr Info...

Clientadapter X8 Intern/Extern

- bis zu 8 PCIe Lanes, 58 Gbit/s

- für Anwendungen inner- und außerhalb des Gehäuses

mehr Info...

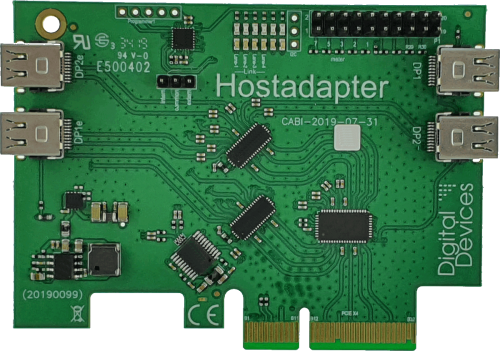

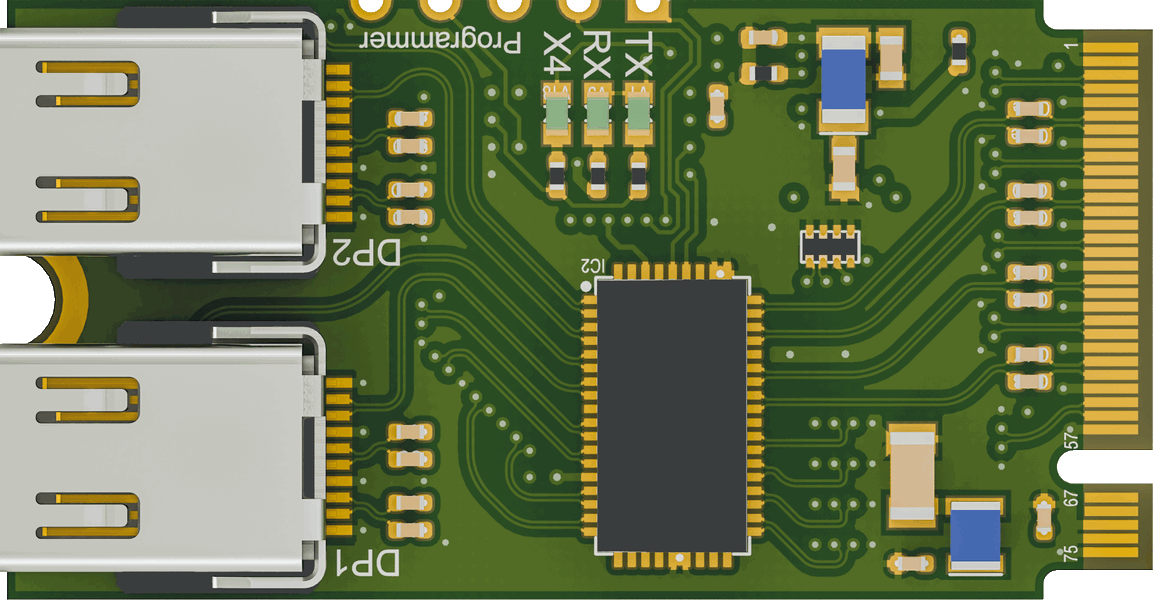

Hostadapter X4 Intern/Extern

- bis zu 4 PCIe Lanes, 32 Gbit/s

- für Anwendungen inner- und außerhalb des Gehäuses

mehr Info...

Hostadapter X8 Intern/Extern

- bis zu 8 PCIe Lanes, 58 Gbit/s

- für Anwendungen inner- und außerhalb des Gehäuses

mehr Info...

Hostadapter M2.M X4

- bis zu 4 PCIe Lanes, 32 Gbit/s

- für Anwendungen inner- und außerhalb des Gehäuses

mehr Info...

Hostadapter M2.E X2

- bis zu 2 PCIe Lanes, 16 Gbit/s

- für Anwendungen inner- und außerhalb des Gehäuses